# CIT 344: INTRODUCTION TO COMPUTER DESIGN

# NATIONAL OPEN UNIVERSITY OF NIGERIA

# FACULTY OF SCIENCE

# **COURSE CODE: CIT344**

# **COURSE TITLE:**

# INTRODUCTION TO COMPUTER DESIGN

# CIT344 INTRODUCTION TO COMPUTER DESIGN

Course Team Adaora Obayi (Developer/Writer) - NOUN Dr. Oyebanji (Programme Leader) - NOUN Vivian Nwaocha (Coordinator) -NOUN

#### *CIT344*

# NATIONAL OPEN UNIVERSITY OF NIGERIA

14/16 Ahmadu Bello Way Victoria Island Lagos

Abuja Office 5, Dar es Salaam Street Off Aminu Kano Crescent Wuse II, Abuja Nigeria

e-m ail: <u>centralinfo@nou.edu.ng</u> URL: <u>www.nou.edu.ng</u>

Published By: National Open University of Nigeria

First Printed 2012

ISBN: 978-058-047-6

All Rights Reserved

# CONTENTS

# PAGE

| Introduction                         | 1 |

|--------------------------------------|---|

| What You Will Learn in This Course   | 1 |

| Course Aim                           | 1 |

| Course Objectives                    | 2 |

| Working through This Course          | 2 |

| Course Materials                     |   |

| Study Units                          | 3 |

| Textbooks and References             | 4 |

| Assignment File                      | 4 |

| Presentation Schedule                |   |

| Assessment                           | 4 |

| Tutor-Marked Assignments (TMAs)      | 4 |

| Final Examination and Grading        | 4 |

| Course Marking Scheme                | 7 |

| Course Overview                      | 7 |

| How to Get the Most from This Course |   |

| Facilitators/Tutors and Tutorials10  | ) |

# Introduction

**CIT344: Introduction to Computer Design** is a 3-credit unit course for students studying towards acquiring the Bachelor of Science in Information Technology and related disciplines.

The course is divided into 6 modules and 21 study units. It introduces you to concepts in Computer Design and their implementations in our everyday lives.

This course also provides information on numbers and codes in computer design, different logic designs, memory devices, microprocessors and finally, a type of programming called Assembly Language Programming.

At the end of this course, it is expected that you should be able to understand, explain and be adequately equipped with comprehensive knowledge of logic designs and can try your hands in some designs of your own.

This course guide therefore gives you an overview of what the course is all about, the textbooks and other course materials to be used, what you are expected to know in each unit, and how to work through the course material.

Furthermore, it suggests the general strategy to be adopted and also emphasises the need for self-assessment and tutor-marked assignment. There are also tutorial classes that are linked to this course and you are advised to attend them.

## What You Will Learn in This Course

The overall aim of this course is to boost your knowledge of logic designs, microprocessors and assembly language programming. In the course of your studies, you will be equipped with definitions of common terms, characteristics and applications of logic designs. You will also learn number systems and codes, memory devices, microprocessors and finally, loops and subroutines in assembly language.

## **Course Aim**

This course aims to give you an in-depth understanding of computer designs. It is hoped that the knowledge would enhance your expertise in logic designs.

# **Course Objectives**

It is relevant to note that each unit has its precise objectives. You should learn them carefully before proceeding to subsequent units. Therefore, it is useful to refer to these objectives in the course of your study of the unit to assess your progress. You should always look at the unit objectives after completing a unit. In this way, you can be sure that you have done what is required of you by the end of the unit. However, below are overall objectives of this course. On successful completion of this course, you should be able to:

- explain the term number system and its various types

- state the various conversion from one number system to the other

- explain the various types of codes

- analyse and design a combinational logic circuit

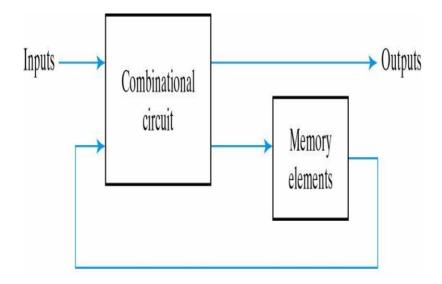

- describe what a sequential logic circuit is

- state the differences between combinational and sequential logic circuit

- list the types of sequential logic circuit

- describe what a latch and flip-flop is

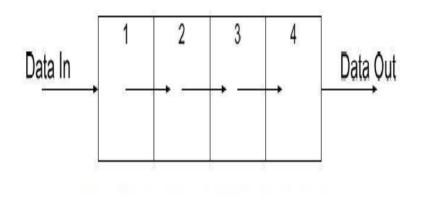

- describe what shift register is

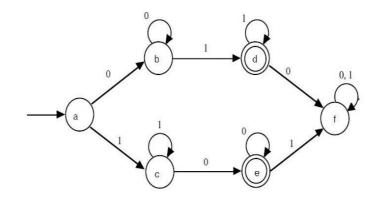

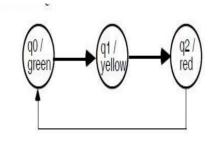

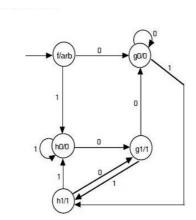

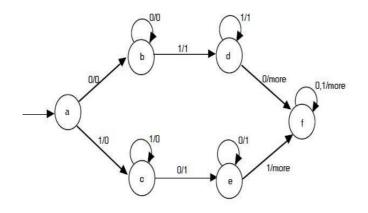

- discuss about finite state machines

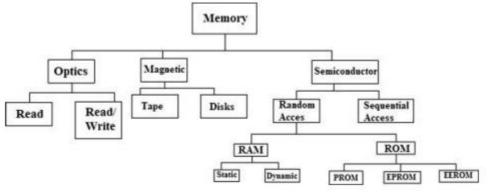

- describe memory and the basic operations performed on it

- state the types of memory we have

- describe microprocessors

- write a program using assembly language.

# Working through This Course

To complete this course, you are required to study all the units, the recommended text books, and other relevant materials. Each unit contains tutor-marked assignments, and at some point in this course, you are required to submit the tutor-marked assignments. There is also a final examination at the end of this course. Stated below are the components of this course and what you have to do.

## **Course Materials**

The major components of the course are:

- 1. Course Guide

- 2. Study Units

- 3. Text Books

- 4. Assignment File

- 5. Presentation Schedule

# **Study Units**

There are 6 modules and 21 study units in this course. They are:

#### Module 1 Introduction to Numbers and Codes

- Unit 1 Types of Number Systems I

- Unit 2 Types of Number Systems II

- Unit 3 Codes

## Module 2 Combinational Logic Design and Application

- Unit 1 Analysis and Design of a Combinational Logic CircuitUnit 2 Typical Combinational Logic Circuit IUnit 3 Typical Combinational Logic Circuit II

- Unit 4 Typical Combinational Logic Circuit III

## Module 3 Sequential Logic Design and Applications

- Unit 1 Sequential Logic Circuits

- Unit 2 Latches and Flip-Flops

- Unit 3 Registers

- Unit 4 Finite State Machines

## Module 4 Memory Devices

- Unit 1 Memory Organisation

- Unit 2 Memory Types

- Unit 3 Memory Expansion

- Unit 4 Memory Summary

#### Module 5 Introduction to Microprocessors

- Unit 1 Microprocessors

- Unit 2 Central Processing Unit and Arithmetic and Logical Unit

- Unit 3 Addressing Mode

#### Module 6 Assembly Language Programming

- Unit 1 Learning to Program with Assembly Language

- Unit 2 Branching Loops and Subroutines

- Unit 3 Sample Programs in Assembly Language

#### **Textbooks and References**

These texts listed below will be of enormous benefit to you in learning this course:

- Elahi A (2018). Computer System: Digital Design, Fundamentals of Computer Architecture and Assembly Language. Springer Nature

- Patt Y. N (2019). Introduction to Computing Systems From Bits and Gates to C and Beyond (Online Version). Mc-Graw-Hill.

- Verma A.K, Shama G and Singh K (2016). Wiley Acing The Gate: Computer Science and Information Technology. Wiley India Pvt. Ltd.

- Mano M.M, Kime C.R and Martin T (2015). Logic & Computer Design Fundamentals (5<sup>th</sup> edition). Pearson. Pg283

- Faroughi N (2015). Digital Logic Design & Computer Organization: With Computer Architecture for Security. McGraw-Hill Education.

- Patterson D. A and Hennessy J.L (2016). *Computer Organization & Design ARM Edition: The Hardware Software Interface*. Morgan Kaufmann.

- Unsalan C and Tar B (2017). Digital System Design with FPGA Implementation Using Verilog and VHDL. McGraw-Hill Education.

- Null L and Lobur J (2016). The Essentials of Computer Organization and Architecture (4<sup>th</sup> edition). Jones & Barlett Learning.

- Rafiquzzaman M (2014). Fundamentals of Digital Logic and Microcontrollers. John Wiley & Sons.

- Roth, H. C. Jr & Kinney, L. L. (2014). *Fundamentals of Logic Design* (7<sup>th</sup> edition). Cengage Learning.

- Tanenbaum, Andrew S. (2013). *Structured Computer Organization*. Prentice Hall (6th ed).

- Mano M.M (2017). Digital Logic and Computer Design. Pearson India Education Services Pvt. Ltd

- Yasin M., Rajendran J. (JV) and Sinanoglu O. (2020). Trustworthy Hardware Design: Combinational Logic Locking TechniquesSpringer Nature

- Ndjountche T. (2016). Digital Electronics 1: Combinational Logic Circuits. Wiley

- Pedroni V.A (2020). Circuit Design with VHDL(3<sup>rd</sup> Edition). The MIT Press Cambridge.

- Sarkar S.K., De A.k., and Sarkar S (2014). Foundation of Digital Electronics and Logic Design. Pan Stanford

Stallings W (2016). Computer Organization and architecture: Designing for Performance (10th

*CIT344* edition). Pearson Education Limited.

Pyeatt L.D and Ughetta W (2020). ARM 64-Bit Assembly Language. Newnes, Elsevier.

- Pyeatt L.D (2016). Modern Assembly Language Programming with the Arm Processor. Newnes, Elsevier

- Schousek T (2018). The Art of Assembly Language Programming using PIC Technology:

Core Fundamentals. Newnes, Elsevier

- Hoey J.V (2019). Beginning x64 Assembly Programming from Novice to AVX Professional. Apress.

- Kusswurm D (2018). Modern X86 Assembly Language Programming (2<sup>nd</sup> edition). Apress.

Irvine K.R (2014). Assembly Language for x86 Processors. Pearson

Dunne R (2018). Windows 64-bit Assembly Language Programming Quick Start. Gaul Communications.

7-segment display. https://www.electronics-tutorials.ws/blog/7-segment-display-tutorial.html

The Evolution of the Revolution: Explore the Intel Technology Innovations that have changed the world <u>http://download.intel.com/pressroom/kits/IntelProcessorHistory.pdf</u>

80x86 Addressing Modes:

https://www.plantationproductions.com/Webster/www.artofasm.com/DOS/ch04/CH04-2.html

www.cs.siu.edu

www.educypedia.be/electronics

www.books.google.com

#### **Assignment File**

The assignment file will be given to you in due course. In this file, you will find all the details of the work you must submit to your tutor for marking. The marks you obtain for these assignments will count towards the final mark for the course. Altogether, there are 21 tutor-marked assignments for this course.

#### **Presentation Schedule**

The presentation schedule included in this course guide provides you with important dates for completion of each tutor-marked assignment. You should therefore endeavour to meet the deadlines.

#### Assessment

There are two aspects to the assessment of this course. First, there are tutor-marked assignments; and second, the written examination.

You are expected to take note of the facts, information and problem solving gathered during the course. The tutor-marked assignments must be submitted to your tutor for formal assessment, in accordance to the deadline given. The work submitted will count for 40% of your total course mark. At the end of the course, you will need to sit for a final written examination. This examination will account for 60% of your total score.

#### **Tutor-Marked Assignments (TMAs)**

There are 21 TMAs in this course. You need to submit all the TMAs. When you have completed each assignment, send them to your tutor as soon as possible and make certain that it gets to your tutor on or before the stipulated deadline. If for any reason you cannot complete your assignment on time, contact your tutor before the assignment is due to discuss the possibility of extension. Extension will not be granted after the deadline, unless in extraordinary cases.

## **Final Examination and Grading**

The final examination for CIT344 will be of last for a period of 3 hours and have a value of 60% of the total course grade. The examination will consist of questions which reflect the self-assessment exercise and tutormarked assignments that you have previously encountered. Furthermore, all areas of the course will be examined. It would be better to use the time between finishing the last unit and sitting for the examination, to revise the entire course. You might find it useful to review your TMAs

and comment on them before the examination. The final examination covers information from all parts of the course.

# **Course Marking Scheme**

The following table includes the course marking scheme

#### Table 1:Course Marking Scheme

| Assessment        | Marks                              |

|-------------------|------------------------------------|

| Assignments 1-21  | 21 assignments, 40% for the best 4 |

|                   | Total = 10% X 4 = 40%              |

| Final Examination | 60% of overall course marks        |

| Total             | 100% of Course Marks               |

## **Course Overview**

This indicates the units, the number of weeks required to complete them and the assignments.

#### Table 2:Course Organiser

| Unit | Title of Work                                         | Weeks<br>Activity | Assessment<br>(End of Unit) |

|------|-------------------------------------------------------|-------------------|-----------------------------|

|      | Course Guide                                          | Week 1            |                             |

|      | Module 1 Introduction to N                            |                   |                             |

| 1    | Types of Number Systems I                             | Week 1            | Assignment 1                |

| 2    | Types of Number Systems II                            | Week 2            | Assignment 2                |

| 3    | Codes                                                 | Week 3            | Assignment 3                |

|      | Module 2 Combinational L                              | ogic Design a     | and Applications            |

| 1    | Analysis & Design of a<br>Combinational Logic Circuit | Week 3            | Assignment 4                |

| 2    | Typical Combinational<br>Logic Circuit I              | Week 4            | Assignment 5                |

| 3    | Typical Combinational Logic<br>Circuit II             | Week 4            | Assignment 6                |

| 4    | Typical Combinational<br>Logic Circuit III            | Week 5            | Assignment 7                |

|      | Module 3 Sequential Logic                             | c Design and      | Applications                |

| 1    | Sequential Logic Circuits                             | Week 5            | Assignment 8                |

| 2    | Latches and Flip-Flops                                | Week 6            | Assignment 9                |

| 3    | Registers                                             | Week 6            | Assignment 10               |

| 4    | Finite State Machines                                 | Week 7            | Assignment 11               |

|                                        | Module 4 Memory Devices   | S             |               |

|----------------------------------------|---------------------------|---------------|---------------|

| 1                                      | Memory Organisation       | Week 7        | Assignment 12 |

| 2                                      | Memory Types              | Week 8        | Assignment 13 |

| 3                                      | Memory Expansion          | Week 9        | Assignment 14 |

| 4                                      | Memory Summary            | Week 10       | Assignment 15 |

| Ι                                      | Module 5Introduction To   | Microprocesso | ors           |

| 1                                      | Microprocessors           | Week 10       | Assignment 16 |

| 2                                      | Central Processing Unit & | Week 11       | Assignment 17 |

|                                        | Arithmetic & Logical Unit |               |               |

| 3                                      | Addressing Mode           | Week 12       | Assignment 18 |

| Module 6 Assembly Language Programming |                           |               | ning          |

| Unit                                   | Learning to Program with  | Week 13       | Assignment 19 |

| 1                                      | Assembly Language         |               |               |

| Unit                                   | Branching Loops and       | Week 14       | Assignment 20 |

| 2                                      | Subroutine                |               |               |

| Unit                                   | Sample Programs in        | Week 14       | Assignment 21 |

| 3                                      | Assembly Language         |               |               |

## How to Get the Most Out of This Course

In distance learning, the study units replace the university lecturer. This is one of the huge advantages of distance learning mode; you can read and work through specially designed study materials at your own pace and at a time and place that is most convenient. Think of it as reading from the teacher, the study guide indicates what you ought to study, how to study it and the relevant texts to consult. You are provided with exercises at appropriate points, just as a lecturer might give you an inclass exercise.

Each of the study units follows a common format. The first item is an introduction to the subject matter of the unit and how a particular unit is integrated with the other units and the course as a whole. Next to this is a set of learning objectives. These learning objectives are meant to guide your studies. The moment a unit is finished, you must go back and check whether you have achieved the objectives. If this is made a habit, then you will increase your chances of passing the course.

The main body of the units also guides you through the required readings from other sources. This will usually be either from a set book or from other sources. Self assessment exercises are provided throughout the unit, to aid personal studies and answers are provided at the end of the unit. Working through these self tests will help you to achieve the objectives of the unit and also prepare you for tutor marked assignments and examinations. You should attempt each self test as you encounter them in the units. Read the course guide thoroughly and organise a study schedule. Refer to the course overview for more details. Note the time you are expected to spend on each unit and how the assignment relates to the units. Important details, e.g. details of your tutorials and the date of the first day of the semester are available. You need to gather together all these information in one place such as a diary, a wall chart calendar or an organiser. Whatever method you choose, you should decide on and write in your own dates for working on each unit.

Once you have created your own study schedule, do everything you can to stick to it. The major reason that students fail is that they get behind with their course works. If you get into difficulties with your schedule, please let your tutor know before it is too late for help.

Turn to unit 1 and read the introduction and the objectives for the unit.

Assemble the study materials. Information about what you need for a unit is given in the table of content at the beginning of each unit. You will almost always need both the study unit you are working on and one of the materials recommended for further readings, on your desk at the same time.

Work through the unit, the content of the unit itself has been arranged to provide a sequence for you to follow. As you work through the unit, you will be encouraged to read from your set books.

Keep in mind that you will learn a lot by doing all your assignments carefully. They have been designed to help you meet the objectives of the course and will help you pass the examination.

Review the objectives of each study unit to confirm that you have achieved them. If you are not certain about any of the objectives, review the study material and consult your tutor.

When you are confident that you have achieved a unit's objectives, you can start on the next unit. Proceed unit by unit through the course and try to pace your study so that you can keep yourself on schedule.

When you have submitted an assignment to your tutor for marking, do not wait for its return before starting on the next unit. Keep to your schedule. Pay particular attention to your tutor's comments on the tutormarked assignment form and also written on the assignment when the assignment is returned to you. Consult you tutor as soon as possible if you have any questions or problems. After completing the last unit, review the course and prepare yourself for the final examination. Check that you have achieved the unit objectives (listed at the beginning of each unit) and the course objectives (listed in this course guide).

# **Facilitators/Tutors and Tutorials**

There are 8 hours of tutorial provided in support of this course. You will be notified of the dates, time and location together with the name and phone number of your tutor as soon as you are allocated a tutorial group.

Your tutor will mark and comment on your assignments, keep a close watch on your progress and on any difficulties you might encounter and provide assistance to you during the course. You must mail your tutor marked assignment to your tutor well before the due date. At least two working days are required for this purpose. They will be marked by your tutor and returned to you as soon as possible. Do not hesitate to contact your tutor by telephone, e-mail or discussion board if you need help. The following might be circumstances in which you would find help necessary:

- you do not understand any part of the study units or the assigned readings

- you have difficulty with the self test or exercise

- you have questions or problems with an assignment, with your tutor's comments on an assignment or with the grading of an assignment.

You should try your best to attend the tutorials. This is the only chance to have face-to-face contact with your tutor and ask questions which are answered instantly. You can raise any problem encountered in the course of your study. To gain the maximum benefit from the course tutorials, prepare a question list before attending them. You will learn a lot from participating actively in tutorial discussions. Course CodeCIT344Course TitleIntroduction to Computer Design

Course Team Adaora Obayi (Developer/Writer) - NOUN Dr. Oyebanji (Programme Leader) - NOUN Vivian Nwaocha (Coordinator) -NOUN

National Open University of Nigeria Headquarters 14/16 Ahmadu Bello Way Victoria Island Lagos

Abuja Office 5, Dar es Salaam Street Off Aminu Kano Crescent Wuse II, Abuja Nigeria

e-mail: <u>centralinfo@nou.edu.ng</u> URL: <u>www.nou.edu.ng</u>

Published By: National Open University of Nigeria

First Printed 2012

ISBN: 978-058-047-6

All Rights Reserved

# CONTENTS

# PAGE

| Module 1                                                                             | Introduction to Numbers and Codes                                                                                                                                                                          | 1                                                                                                     |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Unit 1                                                                               | Types of Number Systems I                                                                                                                                                                                  | 1                                                                                                     |

| Unit 2                                                                               | Types of Number Systems I                                                                                                                                                                                  | 11                                                                                                    |

| Unit 3                                                                               | Unsigned and Signed Binary Numbers                                                                                                                                                                         | 21                                                                                                    |

| Unit 3                                                                               | Codes                                                                                                                                                                                                      | 31                                                                                                    |

| Module 2                                                                             | Combinational Logic Design and Application                                                                                                                                                                 | 38                                                                                                    |

| Unit 1                                                                               | Analysis and Design of a Combinational Logic Circuit                                                                                                                                                       | 38                                                                                                    |

| Unit 2                                                                               | Typical Combinational Logic Circuit I                                                                                                                                                                      |                                                                                                       |

| Unit 3                                                                               | Typical Combinational Logic Circuit II                                                                                                                                                                     |                                                                                                       |

| Unit 4                                                                               | Typical Combinational Logic Circuit III                                                                                                                                                                    | 61                                                                                                    |

| Module 3                                                                             | Sequential Logic Design and Applications                                                                                                                                                                   | 60                                                                                                    |

| Unit 1                                                                               | Sequential Logic Circuits                                                                                                                                                                                  | 60                                                                                                    |

| Unit 2                                                                               | Latches and Flip-Flops                                                                                                                                                                                     | 65                                                                                                    |

| Unit 3                                                                               | Registers                                                                                                                                                                                                  | 90                                                                                                    |

| Unit 4                                                                               | Finite State Machines                                                                                                                                                                                      | 105                                                                                                   |

| Module 4                                                                             | Memory Devices                                                                                                                                                                                             | 126                                                                                                   |

| Unit 1                                                                               | Memory Organisation                                                                                                                                                                                        | 126                                                                                                   |

| TT '/ O                                                                              | Memory Types                                                                                                                                                                                               | 135                                                                                                   |

| Unit 2                                                                               |                                                                                                                                                                                                            | 155                                                                                                   |

| Unit 2<br>Unit 3                                                                     | Memory Expansion                                                                                                                                                                                           | 150                                                                                                   |

|                                                                                      |                                                                                                                                                                                                            |                                                                                                       |

| Unit 3                                                                               | Memory Expansion                                                                                                                                                                                           | 150                                                                                                   |

| Unit 3<br>Unit 4                                                                     | Memory Expansion<br>Memory Summary                                                                                                                                                                         | 150<br>154                                                                                            |

| Unit 3<br>Unit 4<br>Module 5                                                         | Memory Expansion.         Memory Summary.         Introduction to Microprocessors.         Microprocessors.         Central Processing Unit and Arithmetic and Logical                                     | 150<br>154<br><b>157</b><br>157                                                                       |

| Unit 3<br>Unit 4<br><b>Module 5</b><br>Unit 1<br>Unit 2                              | Memory Expansion<br>Memory Summary<br>Introduction to Microprocessors<br>Microprocessors<br>Central Processing Unit and Arithmetic and Logical<br>Unit                                                     | 150<br>154<br><b>157</b><br>157<br>165                                                                |

| Unit 3<br>Unit 4<br><b>Module 5</b><br>Unit 1                                        | Memory Expansion<br>Memory Summary<br>Introduction to Microprocessors<br>Microprocessors<br>Central Processing Unit and Arithmetic and Logical                                                             | 150<br>154<br><b>157</b><br>157                                                                       |

| Unit 3<br>Unit 4<br><b>Module 5</b><br>Unit 1<br>Unit 2                              | Memory Expansion<br>Memory Summary<br>Introduction to Microprocessors<br>Microprocessors<br>Central Processing Unit and Arithmetic and Logical<br>Unit                                                     | 150<br>154<br><b>157</b><br>157<br>165<br>175                                                         |

| Unit 3<br>Unit 4<br><b>Module 5</b><br>Unit 1<br>Unit 2<br>Unit 3                    | Memory Expansion<br>Memory Summary<br>Introduction to Microprocessors<br>Microprocessors<br>Central Processing Unit and Arithmetic and Logical<br>Unit<br>Addressing Mode                                  | <ul> <li>150</li> <li>154</li> <li>157</li> <li>157</li> <li>165</li> <li>175</li> <li>188</li> </ul> |

| Unit 3<br>Unit 4<br><b>Module 5</b><br>Unit 1<br>Unit 2<br>Unit 3<br><b>Module 6</b> | Memory Expansion<br>Memory Summary<br>Introduction to Microprocessors<br>Microprocessors<br>Central Processing Unit and Arithmetic and Logical<br>Unit<br>Addressing Mode<br>Assembly Language Programming | 150<br>154<br><b>157</b><br>157<br>165<br>175<br><b>188</b><br>. 188                                  |

# MODULE 1 INTRODUCTION TO NUMBERS AND CODES

- Unit 1 Types of Number Systems I

- Unit 2 Types of Number Systems II

- Unit 3 Unsigned and Signed Binary Numbers

- Unit 4 Codes

# UNIT 1 TYPES OF NUMBER SYSTEMS I

## CONTENTS

- 1.0 Introduction

- 2.0 Intended Learning Outcomes (ILOs)

- 3.0 Main Content

- 3.1 Decimal Number System

- 3.2 Binary Number System

- 3.2.1 Fractions in Binary Number System

- 3.2.2 Binary Arithmetic

- 3.2.3 Binary to Decimal Conversion

- 3.2.4 Decimal to Binary Conversion

- 4.0 Self-Assessment Exercise(s)

- 5.0 Conclusion

- 6.0 Summary

- 7.0 Further Readings

# 1.0 Introduction

The number system is the basis of computing. It is a very important foundation for understanding the way the computer system works. In this unit, we will talk about decimal and binary number system. Endeavour to assimilate as much as possible from this unit – especially, the conversion from one number system to another.

# 2.0 Intended Learning Outcomes (ILOs)

At the end of this unit, you should be able to:

- explain the term decimal number system

- manipulate fractions of decimal numbers

- explain the term binary number system

- manipulate binary arithmetic

- convert binary to decimal

- convert decimal to binary

# 3.0 Main Content

## 3.1 Decimal Number System

The decimal number has a base or radix of 10 meaning that it, has 10 allowable digits ranging from 0 through 9. Thus, the ten unique digits are as follows: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. Using these single digits, ten different values can be represented and also forms the basis for counting as every other number above digit 9 is gotten from systematically combining two or more of the single digits together. Thus, ten is represented by the combination of "1" and "0"digits resulting to number 10, two hundred seventy five is represented by 275, etc. The decimal number system is a positional number system as the position of a digit represents its true magnitude. For example, 2 is less than 7, however 2 in 275 represents 200, whereas 7 represents 70. The left most digit has the highest weight and the right most digit has the lowest weight. 275 can be written in the form of an expression in terms of the base value of the number system and weights.

2 x 102 + 7 x 101 + 5 x 100 = 200 + 70 + 5 = 275

where, 10 represents the base or radix,102, 101, 100 represent the weights 100, 10 and 1 of the numbers 2, 7 and 5. Hence the general equation form any number system is given as:

$(a_5a_4a_3a_2a_1a_0a_{-1}a_{-2}a_{-3})_r = (a_i)_r$ Where r is the base and  $a_i$  must be less than r

#### **Fractions in Decimal Number System**

In a Decimal Number System the fraction part is separated from the integer part by a decimal point. The integer part of a number is written on the left hand side of the decimal point. The fraction part is written on the right side of the decimal point. The digits of the integer part on the left hand side of the decimal point have weights 100, 101, 102 etc. respectively starting from the digit to the immediate left of the decimal point and moving away from the decimal point towards the most significant digit on the left hand side. Fractions in decimal number system are also represented in terms of the base value of the number system and weights. The weights of the fraction part are represented by 10-1, 10-2, 10-3, etc. The weights decrease by a factor of 10 moving right of the decimal point. The number 382.91 in terms of the base number and weights is represented as

$3 \ge 102 + 8 \ge 101 + 2 \ge 100 + 9 \ge 10^{-1} + 1 \ge 10^{-2} = 300 + 80 + 2 + 0.9 + 0.01 = 382.91$

# 3.2 Binary Number System

Binary as the name indicates is a base-2 number system having only two numbers 0 and 1. The binary digit 0 or 1 is known as a 'Bit'. Below is the decimal equivalent of the binary number system.

| Decimal | Binary | Decimal | Binary |

|---------|--------|---------|--------|

| Number  | Number | Number  | Number |

| 0       | 0      | 10      | 1010   |

| 1       | 1      | 11      | 1011   |

| 2       | 10     | 12      | 1100   |

| 3       | 11     | 13      | 1101   |

| 4       | 100    | 14      | 1110   |

| 5       | 101    | 15      | 1111   |

| 6       | 110    | 16      | 10000  |

| 7       | 111    | 17      | 10001  |

| 8       | 1000   | 18      | 10010  |

| 9       | 1001   | 19      | 10011  |

|         |        | 20      | 10100  |

Table 1: Decimal Equivalents of Binary Number System

Counting in binary number system is similar to counting in decimal number systems. In a decimal number system a value larger than 9 has to be represented by 2, 3, 4, or more digits. Similarly, in the binary number system a binary number larger than 1 has to be represented by 2, 3, 4, or more binary digits.

Any binary number comprising of binary 0 and 1 can be easily represented in terms of its decimal equivalent by writing the binary number in the form of an expression using the base value 2 and weights 20, 21, 22, etc.

The number  $10011_2$  (the subscript 2 indicates that the number is a binary number and not a decimal number ten thousand and eleven) can be rewritten in terms of the expression:

$10011_{2} = (1 x 24) + (0 x 23) + (0 x 22) + (1 x 21) + (1 x 20)$ = (1 x 16) + (0 x 8) + (0 x 4) + (1 x 2) + (1 x 1) = 16 + 0 + 0 + 2 + 1 = 19

# 3.2.1 Fractions in Binary Number System

In a decimal number system the integer part and the fraction part of a number are separated by a decimal point. In a binary number system the integer part and the Fraction part of a binary number can be similarly represented separated by a decimal point. The binary number  $1011.101_2$  has an integer part represented by 1011 and a fraction part 101 separated by a decimal point. The subscript 2 indicates that the number is a binary number and not a decimal number. The binary number  $1011.101_2$  can be written in terms of an expression using the base value 2 and weights 23, 22, 21, 20,  $2^{-1}$ ,  $2^{-2}$  and  $2^{-3}$ .

$1011.101_{2} = (1 x 23) + (0 x 22) + (1 x 21) + (1 x 20) + (1 x 2<sup>-1</sup>) + (0 x 2<sup>-2</sup>) + (1 x 2<sup>-3</sup>) = (1 x 8) + (0 x 4) + (1 x 2) + (1 x 1) + (1 x 1/2) + (0 x 1/4) + (1 x 1/8) = 8 + 0 + 2 + 1 + 0.5 + 0 + 0.125 = 11.625$

Computers do handle numbers such as 11.625 that have an integer part and a fraction part. However, it does not use the binary representation 1011.101. Such numbers are represented and used in floating-point numbers notation.

## **3.2.2 Binary Arithmetic**

Digital systems use the binary number system to represent numbers. Therefore these systems should be capable of performing standard arithmetic operations on binary numbers.

#### **Binary Addition**

Binary addition is identical to decimal addition. By adding two binary bits, a sum bit and a carry bit are generated. The only difference between the two additions is the range of numbers used. In binary addition, four possibilities exist when two single bits are added together. The four possible input combinations of two single bit binary numbers and their corresponding sum and carry outputs are specified in Table 2.

| First Number | Second Number | Sum | Carry |

|--------------|---------------|-----|-------|

| 0            | 0             | 0   | 0     |

| 0            | 1             | 1   | 0     |

| 1            | 0             | 1   | 0     |

| 1            | 1             | 0   | 1     |

Table 2: Addition of Two Single Bit Binary Numbers

The first three additions give a result 0, 1 and 1 respectively which can be represented by a single binary digit (bit). The fourth addition results in the number 2, which can be represented in binary as 102. Thus, two digits (bits) are required. This is similar to the addition of 9 + 3 in decimal. The answer is 12 which cannot be represented by a single digit; thus, two digits are required. The number 2 is the sum part and 1 is the carry part.

Any number of binary numbers having any number of digits can be added together.

#### **Binary Subtraction**

Binary subtraction is identical to decimal subtraction. The only difference between the two is the range of numbers. Subtracting two single bit binary numbers results in a difference bit and a borrow bit. The four possible input combinations of two single bit binary numbers and their corresponding difference and borrow outputs are specified in Table 3. It is assumed that the second number is subtracted from the first number.

| First Number | Second Number | Difference | Borrow |

|--------------|---------------|------------|--------|

| 0            | 0             | 0          | 0      |

| 0            | 1             | 1          | 1      |

| 1            | 0             | 1          | 0      |

| 1            | 1             | 0          | 0      |

The second subtraction subtracts 1 from 0 for which a borrow is required to make the first digit equal to 2. The difference is 1. This is similar to decimal subtraction when 17 is subtracted from 21. The first digit 7 cannot be subtracted from 1, therefore 10 is borrowed from the next significant digit. Borrowing a 10 allows subtraction of 7 from 11 resulting in a difference of 4.

#### **Binary Multiplication**

Binary multiplication is similar to the decimal multiplication except for the range of numbers. Four possible combinations of two single bit binary numbers and their products are listed in table 4.

| First Number | Second Number | Product |

|--------------|---------------|---------|

| 0            | 0             | 0       |

| 0            | 1             | 0       |

| 1            | 0             | 0       |

| 1            | 1             | 1       |

#### Table 4:Multiplication of two Single Bit Binary Numbers

#### **Binary Division**

Division in binary follows the same procedure as in the division of decimal numbers. Fig 1 illustrates the division of binary numbers.

$\begin{array}{r} 10 \\

101 | 1101 \\

101 \\

\hline

101 \\

\hline

011 \\

000 \\

\hline

11

\end{array}$

#### Fig. 1 : Binary Division

#### 3.2.3 Binary to Decimal Conversion

Most real world quantities are represented in decimal number system. Digital systems on the other hand are based on the binary number system. Therefore, when converting from the digital domain to the realworld, binary numbers have to be represented in terms of their decimal equivalents. The method used to convert from binary to decimal is the sum-of-weights method.

#### **Sum-of-Weights Method**

Sum-of-weights as the name indicates sums the weights of the binary digits (bits) of a binary number which is to be represented in decimal. The sum-of-weights method can be used to convert a binary number of any magnitude to its equivalent decimal representation.

In the sum-of-weights method an extended expression is written in terms of the binary base number 2 and the weights of the binary number to be converted. The weights correspond to each of the binary bits which are multiplied by the corresponding binary value.

Binary bits having the value 0 do not contribute any value towards the final sum expression. The binary number  $10110_2$  is therefore written in the form of an expression having weights  $2^0$ ,  $2^1$ ,  $2^2$ ,  $2^3$  and  $2^4$

corresponding to the bits 0, 1, 1, 0 and 1 respectively. Weights  $2^0$  and  $2^3$  do not contribute in the final sum as the binary bits corresponding to these weights have the value 0.

$10110_2 = 1 \times 2^4 + 0 \times 2^3 + 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0$ = 16 + 0 + 4 + 2 + 0 = 22

#### Sum-of-Non-Zero Terms

In the sum-of-weights method, the binary bits 0 do not contribute towards the final sum representing the decimal equivalent. Secondly, the weight of each binary bit increases by a factor of 2 starting with a weight of 1 for the least significant bit. For example, the binary number 101102 has weights  $2^0=1$ ,  $2^1=2$ ,  $2^2=4$ ,  $2^3=8$  and  $2^4=16$  corresponding to the bits 0, 1, 1, 0 and 1 respectively.

The sum-of-non-zero terms method is a quicker method to determine decimal equivalents of binary numbers without resorting to writing an expression. In the sum-of-non-zero terms method, the weights of nonzero binary bits are summed, as the weights of zero binary bits do not contribute towards the final sum representing the decimal equivalent.

The weights of binary bits starting from the right most least significant bit is 1, The next significant bit on the left has the weight 2, followed by 4, 8, 16, 32, etc. corresponding to higher significant bits. In binary number system the weights of successive bits increase by an order of 2 towards the left side and decrease by an order of 2 towards the right side. Thus, a binary number can be quickly converted into its decimal equivalent by adding weights of non-zero terms which increase by a factor of 2. Binary numbers having an integer and a fraction part can similarly be converted into their decimal equivalents by applying the same method.

A quicker method is to add the weights of non-zero terms. Thus, for the numbers:

$10011_2 = 16 + 2 + 1 = 19$ 1011.101\_2 = 8 + 2 + 1 + ½ + 1/8 = 11 + 5/8 = 11.625

# 3.2.4 Decimal to Binary Conversion

Conversion from decimal to binary number system is also essential to represent real-world quantities in terms of binary values. The sum-ofweights and repeated division by 2 methods are used to convert a decimal number to equivalent binary.

#### **Sum-of-Weights**

The sum-of-weights method used to convert binary numbers into their decimal equivalent is based on adding binary weights of the binary number bits. Converting back from the decimal number to the original binary number requires finding the highest weight included in the sum representing the decimal equivalent. A binary 1 is marked to represent the bit which contributed its weight in the sum representing the decimal equivalent. The weight is subtracted from the sum decimal equivalent. The next highest weight included in the sum term is found. A binary 1 is marked to represent the bit which contributed its weight in the sum term is found. A binary 1 is marked to represent the bit which contributed its weight in the sum term and the sum term becomes equal to zero. The binary 1s and 0s represent the binary bits that contributed their weight and bits that did not contribute any weight respectively.

The process of determining binary equivalent of a decimal number 392 and 411 is illustrated in a tabular form.

| Table 5: | Converting Decimal to Binary using Sum-of-Weights |

|----------|---------------------------------------------------|

|          | Method                                            |

| Sum Term | Highest | Binary Number | Sum Term             |

|----------|---------|---------------|----------------------|

|          | Weight  |               | = Sum Term – Highest |

|          |         |               | Weight               |

| 392      | 256     | 10000000      | 136                  |

| 136      | 128     | 11000000      | 8                    |

| 8        | 8       | 110001000     | 0                    |

The sum-of-weights method requires mental arithmetic and is a quick way of converting small decimal numbers into binary. With practice large decimal numbers can be converted into binary equivalents.

#### **Repeated Division-by-2**

Repeated division-by-2 method allows decimal numbers of any magnitude to be converted into binary. In this method, the decimal number to be converted into its binary equivalent is repeatedly divided by 2. The divisor is selected as 2 because the decimal number is being converted into binary a base-2 number system. Repeated division method can be used to convert decimal number into any number system by repeated division by the base-number.

In the repeated-division method the decimal number to be converted is divided by the base number, in this particular case 2. A quotient value and a remainder value is generated, both values are noted done. The remainder value in all subsequent divisions would be either a 0 or a 1. The quotient value obtained as a result of division by 2 is divided again by 2. The new quotient and remainder values are again noted down. In each step of the repeated division method the remainder values are noted down and the quotient values are repeatedly divided by the base number. The process of repeated division stops when the quotient value becomes zero. The remainders that have been noted in consecutive steps are written out to indicate the binary equivalent of the original decimal number.

| Number | Quotient after division | Remainder after division |

|--------|-------------------------|--------------------------|

| 392    | 196                     | 0                        |

| 196    | 98                      | 0                        |

| 98     | 49                      | 0                        |

| 49     | 24                      | 1                        |

| 24     | 12                      | 0                        |

| 12     | 6                       | 0                        |

| 6      | 3                       | 0                        |

| 3      | 1                       | 1                        |

| 1      | 0                       | 1                        |

# Table 6:Converting Decimal to Binary using Repeated<br/>Division by 2 Method

The process of determining the binary equivalent of a decimal number 392 is illustrated in a tabular form above. Reading the numbers in the remainder column from bottom to top 110001000 gives the binary equivalent of the decimal number 392.

# 4.0 Self-Assessment Exercise(s)

Explain with the aid of good examples, the different methods of converting binary numbers to decimal numbers.

# 5.0 Conclusion

The decimal number system has ten unique digits 0, 1, 2, 3... 9. Using these single digits, ten different values can be represented. Values greater than ten can be represented by using the same digits in different combinations. Binary indicates a base-2 number system having only two numbers 0 and 1. The binary digit 0 or 1 is known as a 'Bit'.

#### 6.0 Summary

In this unit, we discussed decimal and binary number systems, manipulation of their fractions, binary arithmetic and conversion of decimal to binary and vice versa. Hoping that you understood the topics discussed, you may now attempt the questions below.

# 7.0 Further Readings

- Elahi A (2018). Computer System: Digital Design, Fundamentals of Computer Architecture and Assembly Language. Springer Nature

- Patt Y. N (2019). Introduction to Computing Systems From Bits and Gates to C and Beyond (Online Version). Mc-Graw-Hill.

- Verma A.K, Shama G and Singh K (2016). Wiley Acing The Gate: Computer Science and Information Technology. Wiley India Pvt. Ltd.

- Mano M.M, Kime C.R and Martin T (2015). Logic & Computer Design Fundamentals (5<sup>th</sup> edition). Pearson. Pg283

- Faroughi N (2015). Digital Logic Design & Computer Organization: With Computer Architecture for Security. McGraw-Hill Education.

- Patterson D. A and Hennessy J.L (2016). *Computer Organization & Design ARM Edition: The Hardware Software Interface*. Morgan Kaufmann.

- Unsalan C and Tar B (2017). Digital System Design with FPGA Implementation Using Verilog and VHDL. McGraw-Hill Education.

- Null L and Lobur J (2016). The Essentials of Computer Organization and Architecture (4<sup>th</sup> edition). Jones & Barlett Learning.

- Rafiquzzaman M (2014). Fundamentals of Digital Logic and Microcontrollers. John Wiley & Sons.

www.cs.siu.edu

www.educypedia.be/electronics

www.books.google.com

#### UNIT 2 TYPES OF NUMBER SYSTEMS II

#### CONTENTS

- 1.0 Introduction

- 2.0 Intended Learning Outcomes (ILOs)

- 3.0 Main Content

- 3.1 Hexadecimal Number System

- 3.1.1 Counting in Hexadecimal Number System

- 3.1.2 Binary to Hexadecimal Conversion

- 3.1.3 Hexadecimal to Binary Conversion

- 3.1.4 Decimal to Hexadecimal Conversion

- 3.1.5 Hexadecimal to Decimal Conversion

- 3.1.6 Hexadecimal Addition and Subtraction

- 3.2 Octal Number System

- 3.2.1 Counting in Octal Number System

- 3.2.2 Binary to Octal Conversion

- 3.2.3 Octal to Binary Conversion

- 3.2.4 Decimal to Octal Conversion

- 3.2.5 Octal to Decimal Conversion

- 3.2.6 Octal Addition and Subtraction

- 4.0 Self- Assessment Exercise(s)

- 5.0 Conclusion

- 6.0 Summary

- 7.0 Further Readings

# .0 Introduction

In this unit we shall conclude with hexadecimal and octal number systems.

# 2.0 Intended Learning Outcomes (ILOs)

At the end of this unit, you should be able to:

- explain the term hexadecimal number system

- count in hexadecimal

- convert binary to hexadecimal

- convert hexadecimal to binary

- convert decimal to hexadecimal

- convert hexadecimal to decimal

- explain hexadecimal addition and subtraction

- explain the term octal number system

- explain hexadecimal addition and subtraction.

# 3.0 Main Content

# 3.1 Hexadecimal Number System

Representing even small number such as 6918 requires a long binary string (1101100000110) of 0s and 1s. Larger decimal numbers would require lengthier binary strings. Writing such long string is tedious and prone to errors.

The hexadecimal number system is a base 16 number system and therefore has 16 digits and is used primarily to represent binary strings in a compact manner. Hexadecimal number system is not used by a digital system. The hexadecimal number system is for our convenience to write binary strings in a short and concise form. Each hexadecimal number digit can represent a 4-bit binary number. The binary numbers and the hexadecimal equivalents are listed below:

| Decimal | Binary | Hexadecimal | Decimal | Binary | Hexadecimal |

|---------|--------|-------------|---------|--------|-------------|

| 0       | 0000   | 0           | 8       | 1000   | 8           |

| 1       | 0001   | 1           | 9       | 1001   | 9           |

| 2       | 0010   | 2           | 10      | 1010   | А           |

| 3       | 0011   | 3           | 11      | 1011   | В           |

| 4       | 0100   | 4           | 12      | 1100   | C           |

| 5       | 0101   | 5           | 13      | 1101   | D           |

| 6       | 0110   | 6           | 14      | 1110   | Е           |

| 7       | 0111   | 7           | 15      | 1111   | F           |

Table 1: Hexadecimal Equivalents of Decimal and Binary Numbers

# 3.1.1 Counting in Hexadecimal Number System

Counting in hexadecimal is similar to the other number systems already discussed. The maximum value represented by a single hexadecimal digit is F which is equivalent to decimal 15. The next higher value decimal 16 is represented by a combination of two hexadecimal digits  $10_{16}$  or 10 H. The subscript 16 indicates that the number is hexadecimal 10 and not decimal 10. Hexadecimal numbers are also identified by appending the character H after the number. The hexadecimal numbers for decimal numbers 16 to 39 are listed below in table 2:

| Decimal | Hexadecimal | Decimal | Hexadecimal | Decimal | Hexadecimal |

|---------|-------------|---------|-------------|---------|-------------|

| 16      | 10          | 24      | 18          | 32      | 20          |

| 17      | 11          | 25      | 19          | 33      | 21          |

| 18      | 12          | 26      | 1A          | 34      | 22          |

| 19      | 13          | 27      | 1B          | 35      | 23          |

| 20      | 14          | 28      | 1C          | 36      | 24          |

| 21      | 15          | 29      | 1D          | 37      | 25          |

| 22      | 16          | 30      | 1E          | 38      | 26          |

| 23      | 17          | 31      | 1F          | 39      | 27          |

#### Table 2: Counting using Hexadecimal Numbers

# 3.1.2 Binary to Hexadecimal Conversion

Converting binary to hexadecimal is a very simple operation. The binary string is divided into small groups of 4-bits starting from the least significant bit. Each 4-bit binary group is replaced by its hexadecimal equivalent.

11010110101110010110 binary number 1101 0110 1011 1001 0110 Dividing into groups of 4-bits

D 6 B 9 6 Replacing each group by its hexadecimal equivalent

Thus, 11010110101110010110 is represented in hexadecimal by D6B96

Binary strings which cannot be exactly divided into a whole number of 4-bit groups are assumed to have 0's appended in the most significant bits to complete a group.

1101100000110 Binary Number

1 1011 0000 0110 Dividing into groups of 4-bits

0001 1011 0000 0110 Appending three 0s to complete the group

1 B 0 6 Replacing each group by its hexadecimal equivalent

# 3.1.3 Hexadecimal to Binary Conversion

Converting from Hexadecimal back to binary is also very simple. Each digit of the hexadecimal number is replaced by an equivalent binary string of 4-bits.

#### F D 1 3 hexadecimal number

1111 1101 0001 0011 Replacing each hexadecimal digit by its 4-bit binary equivalent.

## 3.1.4 Decimal to Hexadecimal Conversion

There are two methods to convert from decimal to hexadecimal. The first method is the indirect method and the second method is the repeated division method.

#### **Indirect Method**

A decimal number can be converted into its hexadecimal equivalent indirectly by first converting the decimal number into its binary equivalent and then converting the binary to Hexadecimal.

#### **Repeated Division-by-16 Method**

The repeated division method has been discussed earlier and used to convert decimal numbers to binary by repeatedly dividing the decimal number by 2. A decimal number can be directly converted into hexadecimal by using repeated division. The decimal number is continuously divided by 16 (base value of the hexadecimal number system).

The conversion of decimal 2096 to hexadecimal using the repeated division-by-16 method is illustrated in Table 3. The hexadecimal equivalent of  $2096_{10}$  is  $830_{16}$ .

# Table 3:Hexadecimal Equivalent of Decimal Numbers Using<br/>Repeated Division

| Number | Quotient after division | Remainder after division |

|--------|-------------------------|--------------------------|

| 2096   | 131                     | 0                        |

| 131    | 8                       | 3                        |

| 8      | 0                       | 8                        |

#### 3.1.5 Hexadecimal to Decimal Conversion

Converting hexadecimal numbers to decimal is done using two methods. The first method is the indirect method and the second method is the sum-of-weights method.

### **Indirect Method**

The indirect method of converting hexadecimal number to decimal number is to first convert hexadecimal number to binary and then binary to decimal.

#### **Sum-of-Weights Method**

A hexadecimal number can be directly converted into decimal by using the sum of weights method. The conversion steps using the sum-ofweights method are shown.

CA02 hexadecimal number C x  $16^3 + A x 16^2 + 0 x 16^1 + 2 x 16^0$  Writing the number in an expression (C x 4096) + (A x 256) + (0 x 16) + (2 x 1) (12 x 4096) + (10 x 256) + (0 x 16) + (2 x 1) Replacing hexadecimal values with decimal equivalents 49152 + 2560 + 0 + 2 Summing the weights 51714 Decimal equivalent

## 3.1.6 Hexadecimal Addition and Subtraction

Numbers represented in hexadecimal can be added and subtracted directly without having to convert them into decimal or binary equivalents. The rules of addition and subtraction that are used to add and subtract numbers in decimal or binary number systems apply to hexadecimal addition and subtraction. Hexadecimal addition and subtractions allows large binary numbers to be quickly added and subtracted.

#### **Hexadecimal Addition**

Carry1Number 12 AC 6Number 29 2 B 5SumB D 7 B

#### **Hexadecimal Subtraction**

Borrow

1

1

1

Number 1

9

2

B

5

Number 2

2

A

C

6

Difference

6

7

E

F

# 3.2 Octal Number System

Octal number system also provides a convenient way to represent long string of binary numbers. The octal number is a base 8 number system with digits ranging from 0 to 7. Octal number system was prevalent in earlier digital systems and is not used in modern digital systems especially when the hexadecimal number is available. Each octal number digit can represent a 3-bit binary number. The binary numbers and the octal equivalents are listed below

| Decimal | Binary | Octal |

|---------|--------|-------|

| 0       | 000    | 0     |

| 1       | 001    | 1     |

| 2       | 010    | 2     |

| 3       | 011    | 3     |

| 4       | 100    | 4     |

| 5       | 101    | 5     |

| 6       | 110    | 6     |

| 7       | 111    | 7     |

Table 4: Octal Equivalents of Decimal and Binary Numbers

# 3.2.5 Counting in Octal Number System

Counting in octal is similar to counting in any other number system. The maximum value represented by a single octal digit is 7. For representing larger values a combination of two or more octal digits has to be used. Thus, decimal 8 is represented by a combination of  $10_8$ . The subscript 8 indicates the number is octal 10 and not decimal ten. The octal numbers for decimal numbers 8 to 30 are listed below:

| Decimal | Octal | Decimal | Octal | Decimal | Octal |

|---------|-------|---------|-------|---------|-------|

| 8       | 10    | 16      | 20    | 24      | 30    |

| 9       | 11    | 17      | 21    | 25      | 31    |

| 10      | 12    | 18      | 22    | 26      | 32    |

| 11      | 13    | 19      | 23    | 27      | 33    |

| 12      | 14    | 20      | 24    | 28      | 34    |

| 13      | 15    | 21      | 25    | 29      | 35    |

| 14      | 16    | 22      | 26    | 30      | 36    |

| 15      | 17    | 23      | 27    | 31      | 37    |

Table 5: Counting using Octal Numbers

# 3.2.6 Binary to Octal Conversion

Converting binary to octal is a very simple. The binary string is divided into small groups of 3-bits starting from the least significant bit. Each 3-bit binary group is replaced by its octal equivalent.

Thus, 111010110101110010110 is represented in octal by 7265626

Binary strings which cannot be exactly divided into a whole number of 3-bit groups are assumed to have 0's appended in the most significant bits to complete a group.

1101100000110Binary number1 101 100 000 110Dividing into groups of 3-bits001 101 100 000110Appending three 0s to complete the group1 5 4 06Replacing each group by its octal equivalent

## 3.2.7 Octal to Binary Conversion

Converting from octal back to binary is also very simple. Each digit of the octal number is replaced by an equivalent binary string of 3-bits.

1 7 2 6 Octal number

001 111 010 110 Replacing each octal digit by its 3-bit binary equivalent.

# 3.2.8 Decimal to Octal Conversion

There are two methods to convert from decimal to octal. The first method is the

Indirect Method and the second method is the repeated division method.

#### **Indirect Method**

A decimal number can be converted into its octal equivalent indirectly by first converting the decimal number into its binary equivalent and then converting the binary to octal.

### **Repeated Division-by-8 Method**

The repeated division method has been discussed earlier and used to convert decimal numbers to binary and hexadecimal by repeatedly dividing the decimal number by 2 and 16 respectively. A decimal number can be directly converted into octal by using repeated division. The decimal number is continuously divided by 8 (base value of the Octal number system).

The conversion of decimal 2075 to octal using the repeated division-by-8 method is illustrated in Table 6. The octal equivalent of  $2075_{10}$  is  $4033_8$ .

Table 6:Octal Equivalent of Decimal Numbers Using Repeated<br/>Division

| Number | Quotient after Division | Remainder after Division |

|--------|-------------------------|--------------------------|

| 2075   | 259                     | 3                        |

| 259    | 32                      | 3                        |

| 32     | 4                       | 0                        |

| 4      | 0                       | 4                        |

#### 3.2.5 Octal to Decimal Conversion

Converting octal numbers to decimal is done using two methods. The first method is the indirect method and the second method is the sum-of-weights method.

#### **Indirect Method**

The indirect method of converting octal number to decimal number is to first convert octal number to binary and then binary to decimal.

#### **Sum-of-Weights Method**

An octal number can be directly converted into decimal by using the sum of weights method. The conversion steps using the sum-of-weights method are shown.

4033 octal number  $4 \ge 8^3 + 0 \ge 8^2 + 3 \ge 8^1 + 3 \ge 8^0$  Writing the number in an expression  $(4 \ge 512) + (0 \ge 64) + (3 \ge 8) + (3 \ge 1)$ 2048 + 0 + 24 + 3 Summing the weights 2075 Decimal equivalent

# 3.2.6 Octal Addition and Subtraction

Numbers represented in octal can be added and subtracted directly without having to convert them into decimal or binary equivalents. The rules of addition and subtraction that are used to add and subtract numbers in decimal or binary number systems apply to octal addition and subtraction. Octal addition and subtractions allows large binary numbers to be quickly added and subtracted.

#### 1. Octal Addition

Carry1Number 17 6 0 2Number 25 7 7 1Sum1 5 5 7 3

## 2. Octal Subtraction

Borrow

1 1

Number 1

7 6 0 2

Number 2

5 7 7 1

Difference

1 6 1 1

## 4.0 Self-Assessment Exercise(s)

Explain how you can convert hexadecimal and octal numbers to binary and decimal numbers and vice versa.

#### 5.0 Conclusion

In this unit we talked about hexadecimal and octal number systems, counting in hexadecimal and octal, hexadecimal & octal arithmetic, conversion of hexadecimal to binary and vice versa, hexadecimal to decimal and vice versa.

## 6.0 Summary

In this unit we talked about hexadecimal and octal number systems, counting in hexadecimal and octal, hexadecimal and octal arithmetic, conversion of hexadecimal to binary and vice versa, hexadecimal to decimal and vice versa.

# 7.0 Further Readings

- Elahi A (2018). Computer System: Digital Design, Fundamentals of Computer Architecture and Assembly Language. Springer Nature

- Patt Y. N (2019). Introduction to Computing Systems From Bits and Gates to C and Beyond (Online Version). Mc-Graw-Hill.

- Verma A.K, Shama G and Singh K (2016). Wiley Acing The Gate: Computer Science and Information Technology. Wiley India Pvt. Ltd.

- Mano M.M, Kime C.R and Martin T (2015). Logic & Computer Design Fundamentals (5<sup>th</sup> edition). Pearson. Pg283

- Faroughi N (2015). Digital Logic Design & Computer Organization: With Computer Architecture for Security. McGraw-Hill Education.

- Patterson D. A and Hennessy J.L (2016). *Computer Organization & Design ARM Edition: The Hardware Software Interface*. Morgan Kaufmann.

- Unsalan C and Tar B (2017). Digital System Design with FPGA Implementation Using Verilog and VHDL. McGraw-Hill Education.

- Null L and Lobur J (2016). The Essentials of Computer Organization and Architecture (4<sup>th</sup> edition). Jones & Barlett Learning.

- Rafiquzzaman M (2014). Fundamentals of Digital Logic and Microcontrollers. John Wiley & Sons.

www.cs.siu.edu www.educypedia.be/electronics www.books.google.com

# UNIT 3 Unsigned and Signed Binary Numbers

# CONTENTS

- 1.0 Introduction

- 2.0 Objectives

- 3.0 Main Content

- 3.1 Unsigned and Signed Binary Numbers

- 3.1.1 Singed-magnitude approach

- 3.1.2 Complements Techniques

- 3.1.3 One's complement addition and subtraction

- 3.1.4 Two's complement addition and subtraction

- 4.0 Conclusion

- 5.0 Summary

- 6.0 Tutor-Marked Assignment

- 7.0 References/Further Reading

#### We will be considering in this unit the unsigned and signed binary number operations and usefulness in computing. Although, brief introduction to complements of numbers generally with few examples will be highlighted but more emphasis will be on binary number operations because that forms the basis of our modern computer designs.

At the end of this unit, you should be able to:

- understand the concept of signed and unsigned number representations

- understand the concept of complement techniques

- understand how computers performs arithmetic operations

# 3.0 Main Content

# 3.1 Unsigned and Signed Binary Numbers

We have looked at the decimal number system and the binary number system in the previous units, but it is also important for us to understand how each of the number systems mentioned above could be represented using signs.

An unsigned decimal or binary number has no arithmetic sign and is always positive. Examples of unsigned decimal number are the numbers on your mobile phone keypads,

your age and many more one can think of without sign. Also, an 8-bit unsigned binary integer are numbers represented from  $00_{16}$  through FF<sub>16</sub> ( $0_{10}$  through 255<sub>10</sub>).

In sign magnitude representation, plus (+) and minus (-) signs are used to represent signed decimal numbers while in binary, we use 0 for positive and 1 for negative binary signed representation. However, every signed representation is always placed to the left side of the number for instance, in binary system, '0' and '1' is placed to the left of the most significant bit position to represent negative and positive number respectively. In other words, the extra bit (0 or 1) placed at the left side of the Most Significant Digit (MSD), represents the sign of the binary number.

| Examp                    | ole            | Magnitude                                                        |

|--------------------------|----------------|------------------------------------------------------------------|

| +210-                    | 0<br>↓<br>Sign | $\begin{bmatrix} & & \\ & & \\ & & \\ 0 & 1 & 0_2 \end{bmatrix}$ |

| <b>-</b> 2 <sub>10</sub> | 1              | 0 1 02                                                           |

| -25 <sub>10</sub>        | 0              | 001 1001 <sub>2</sub>                                            |

| +2510                    | 1              | 001 1001 <sub>2</sub>                                            |

Table 1 shows 4-bit integers represented in Sign-magnitude form. With four bits, we can only represent numbers ranging from  $-7 \le a \le +7$ . In general, if there are n bits of a binary number, it then means that its range spans from within  $\pm (2^{n-1} - 1)$ . This means that with n - 1 bits, accommodates any value from 0 to  $2^{n-1}$  (can be comfortably represented). Although, with this position, it then means that the value zero (0) will then have two representation (i.e 0000 for +0 and 1000 for -0) which sometimes appears confusing in the eye of the reader. This is because in binary, "1000" represents the number eight (8) in decimal but once clearly specified as signed bit then "1000" is now a negative zero (-0).

In complement approach, positive numbers are represented the same manner as they do in sign-magnitude representation whereas, negative numbers have different representation.

| Four-bit integers | Interpretation using sign- |

|-------------------|----------------------------|

| 2                 | magnitude                  |

| 0000              | +0                         |

| 0001              | +1                         |

| 0010              | +2                         |

| 0011              | +3                         |

| 0100              | +4                         |

| 0101              | +5                         |

| 0110              | +6                         |

| 0111              | +7                         |

| 1000              | -0                         |

| 1001              | -1                         |

| 1010              | -2                         |

| 1011              | -3                         |

| 1100              | -4                         |

| 1101              | -5                         |

| 1110              | -6                         |

| 1111              | -7                         |

## Table 1: Sign-magnitude of 4-bit integer representation

## **3.1.2 Complement Techniques**

The complement of a number X, always denoted as  $\overline{X}$  is obtained from X by taking its bit-by-bit complement. In essence, each 0 in X is changed to 1 and each 1 in X is changed to 0.

Example: find the complements of the following binary numbers:

- $1100101_2 == 0011010_2$

- $000111_2 === 111000_2$

- $111111_2 === 000000_2$

Before we proceed further with binary complements, it would be rather necessary we look at how to obtain the complements of some decimal numbers.

## 9's Complement

The 9's complement of a decimal number is obtained by subtracting each digit of the number from 9. Table 2, shows the decimal numbers 0 to 9 and its equivalent 9's complements.

| Decimal | 9's        | Decimal | 9's        |

|---------|------------|---------|------------|

| number  | Complement | number  | Complement |

| 0       | 9          | 5       | 4          |

| 1       | 8          | 6       | 3          |

| 2       | 7          | 7       | 2          |

| 3       | 6          | 8       | 1          |

| 4       | 5          | 9       | 0          |

#### Table 2: 9's complements of decimal numbers

## Example

Obtain the 9's complement of the following numbers: (a) 13 (b) 33 (c) 563

| (a) 99 | (b) 9 9 | (c) 999 |

|--------|---------|---------|

| + 13   | + 3 3   | + 563   |

| 8 6    | 66      | 436     |

# 9's Complement Subtraction